kategorier: Udvalgte artikler » Praktisk elektronik

Antal visninger: 12919

Kommentarer til artiklen: 0

Chip 4046 (K564GG1) til enheder med resonansopbevaring - driftsprincippet

Når der oprettes en elektronisk kraftanordning med resonansretention i LC-kredsløbet, er et resonanskontrolkredsløb designet til at synkronisere de modtagne svingninger med kontrolpulser, der kommer fra driveren.

Denne controller's opgave er at holde resonante svingninger i LC-kredsløbet ved at spænde den i tide med sine egne svingninger. For at opnå dette skal controlleren modtage et signal fra sløjfen fra kredsløbet, der indeholder data om den aktuelle frekvens og fase af frie svingninger deri, hvorefter, afhængigt af disse data, opretholder drivertrinnet i synkronisering med disse frekvens og fase, derefter resonansen i kredsløbet gemmes automatisk.

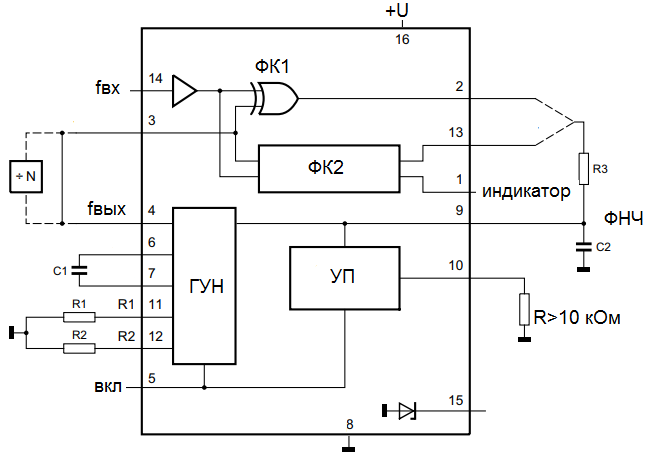

For at bygge en sådan controller er CD4046-chippen eller dens indenlandske modstykke K564GG1 egnet. Lad os se på enheden til denne mikrokredsløb, formålet med dens konklusioner og forbindelsesdiagrammet for de monterede komponenter, for om nødvendigt at forstå, hvad du har at gøre med.

Denne chip giver dig mulighed for nemt at organisere en PLL - faselåst loop. For at opbygge en PLL bruges tre nødvendige blokke, der er placeret inde i mikrokredsløbet: en VCO - spændingsstyret oscillator, en FC - fase komparator og et LPF - lavpasfilter.

Indbygget i mikrokredsløbet genererer VCO en række rektangulære impulser med 50% dækning, det vil sige en ren krumning, hvis indledende frekvens afhænger af parametrene i to RC-kredsløb: R1C1 og R2C2, der er forbundet til den uden for mikrokredsløbet, og amplituden i dette tilfælde er tæt på forsyningsspændingen for mikrokredsløbet U +.

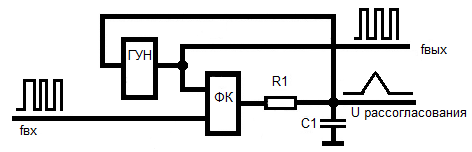

PLL-driftsprincippet

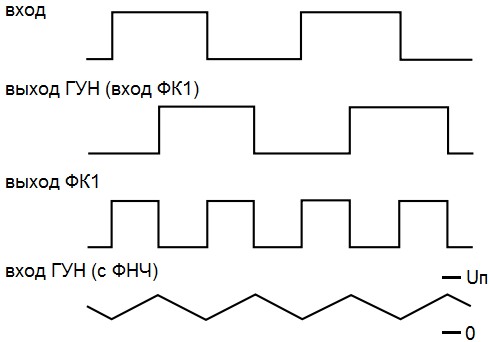

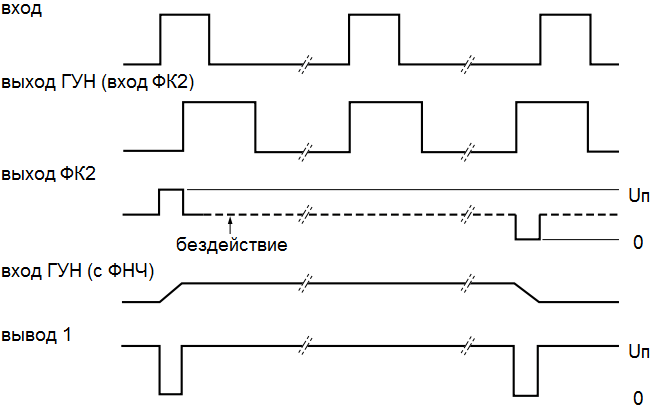

Den eksterne indgangssignalfinne leveres til mikrokredsløbet, faktisk, til en af inputene til fasesammenligningen FC (FC1 eller FC2 - udvikleren vælger) indeni den. Et bugter produceret af VCO føres samtidig til den anden FC-indgang. Som et resultat opnås et rektangulært signal ved FC-udgangen, hvis impulsvarighed afhænger af forskellen mellem pulserne fra VCO og de eksterne pulser på hvert tidspunkt.

Faktisk er varigheden af outputpulserne med FC proportional med faseforskellen mellem de to sammenlignede signaler. Faktum er, at det eksklusive OR-logiske element ofte bruges som en FC, hvilket betyder, at der ved FC-udgangen kun er et højspændingsniveau, hvis der er en forskel mellem signalerne, og hvis der ikke er nogen forskel, vil output fra FC være lav spændingsniveau eller inaktiv tilstand.

Fra FC's udgang føres signalet til et lavpasfilter, som er et simpelt RC-kredsløb, på kondensatoren, hvoraf der opnås en pulserende fejlpasningsspænding, hvor krusningsniveauet er proportionalt med forskellen mellem de to signaler (fra den interne VCO og leveret til mikrokredsløbet udefra), faktisk - faseforskellen .

Den uoverensstemmelsesspænding, der opnås ved LPF-kondensatoren, føres øjeblikkeligt tilbage til VCO-indgangen, og afhængigt af dens gennemsnitsværdi indstilles VCO-frekvensen automatisk, så frekvensen af bølgen ved dens udgang fout nærmer sig frekvensen af det eksterne signal, der kommer fra ydersiden af mikrokredsløbet. Når man når en sådan situation, vil den gennemsnitlige spænding over lavpasfilterets kondensator være den mindste - dette er et tegn på den maksimale konvergens af de to signaler i frekvens og fase. Når signalet således indfanges, vil det fortsat blive holdt af PLL-sløjfen.

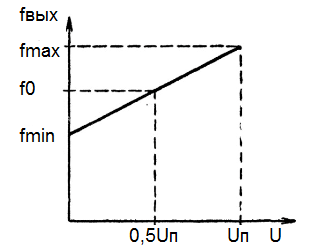

Grænserne for omorganiseringen af VCO

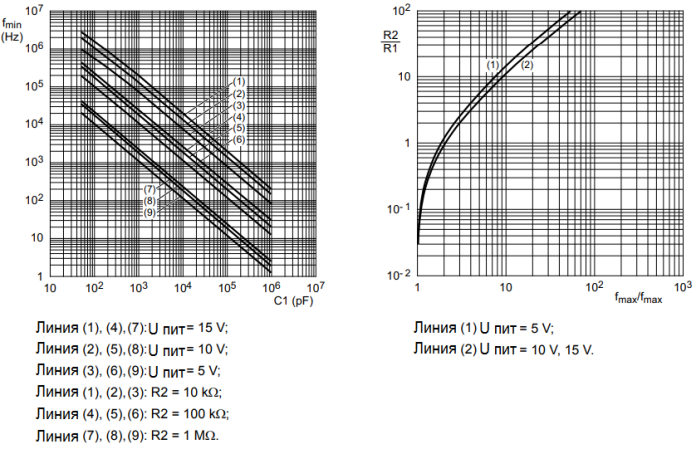

Som du allerede har forstået, er VCO-frekvensen i stand til at indstille inden for et bestemt interval af auto-tuning. Dette interval indstilles af chipens eksterne komponenter. Og reaktionshastigheden for PLL-systemet bestemmes af tidskonstanten for LFF (værdier C2 og R3).Af denne grund skal du strengt nærme valget af monterede komponenter i chippen.

Forsyningsspændingen for mikrokredsløbet, kondensatoren C1 samt modstanderne R1 og R2 bestemmer selvindstillingsområdet for VCO-frekvensen inde i mikrokredsløbet. Modstand R2 forspænder VCO's mindste frekvens fmin over nul. Og forholdet mellem værdierne på modstande R1 og R2 bestemmer forholdet mellem maksimale og minimale frekvenser - fmax / fmin, indstilleligt udgangssignal fra VCO.

Chip indgange og udgange

Konklusion 4 - signaludgang fra VCO, på den i arbejdstilstand meander. Dette output kan bruges til at levere et signal til andre blokke af den designede enhed.

Pin 5 er ansvarlig for at tænde og slukke for VCO. Når der tilføres en højspænding på dette output, slukkes mikrokredsløbet. Ved påføring af et lavspændingsniveau (når du tilslutter stift 5 til fælles ledningen) - fungerer mikrokredsløbet i normal tilstand.

Konklusion 6 og 7. Kondensatoren C1 er forbundet til dem - dette er frekvensindstillende kondensator for VCO.

Konklusion 8 - chipens fælles strømkabel.

Modstand R1 er mellem klemme 11 og fælles ledning. Modstand R2 - mellem klemme 12 og fælles ledning. Dette er frekvensindstillingsmodstande. Modstand R3 for lavpasfilteret - til pin 9 og pin 2 eller 13 (forskellen mellem dem vil blive diskuteret senere), kondensatoren C2 af lowpass filteret er mellem pin 9 og den fælles ledning.

Pin 10 er output fra repeaterforstærkeren. Spændingen på den under driften af mikrokredsløbet er den uoverensstemmende spænding, der leveres til lavpasfilteret. Konklusion 10 er konstrueret således, at fejlpasningsspændingen om nødvendigt let kan isoleres uden at skubbe LPF-kondensatoren. Til denne konklusion er det tilladt at forbinde en modstand med en modstand på mere end 10 kOhm.

Konklusion 15 - på det er katoden af den indbyggede zenerdiode med en stabiliseringsspænding på 5,6 volt (stabiliseringsspændingen for denne zenerdiode kan være anderledes, afhængigt af producenten af chip). Denne zener-diode kan eventuelt bruges i chipets strømkreds.

Konklusion 16 - plus chipens styrke.

Indgange og udgange fra fasesammenligninger FC1 og FC2

Slyngen fra udgangssignalet fra VCO tages fra terminal 4 og føres til terminal 3, forbundet via en forstærker-shaper til indgangene til fasesammenligningerne FC1 og FC2. Om ønsket kan signalet fra VCO eventuelt føres gennem en frekvensdeler.

Input 14 er en signalindgang, og et indgangssignal føres til det, med hvilket det er nødvendigt at synkronisere udgangssignalet ved udgangen fra VCO. Afhængigt af indgangssignalets art kan udvikleren vælge, hvilken af fasekomparatorerne der skal bruges: FC1 eller FC2, og fastgør en lavpas-filtermodstand til den valgte komparator (til pin 2 eller 13). Fase-komparatoren FC2 har en indikatorstift 1, der vises en højspændingsspænding på den, når signalerne maksimalt synkroniseres.

Det særlige ved FC1 er, at det er et simpelt eksklusivt OR-logisk element, og kvaliteten af dets funktion afhænger af parametrene for lavpasfilteret ved dets output. Arbejdet begynder med centerfrekvensen f0 = (fmax-fmin) / 2, det er muligt at fange harmonikerne i centerfrekvensen. Det har høj støjimmunitet.

Det særlige ved FC2 er, at det kun behandler de positive forskelle mellem de impulser, der leveres til det, og pulsenes driftscyklus betyder derfor ikke noget. Arbejdet begynder med en minimumsfrekvens fmin, der er ingen mulighed for at fange harmonikken i den centrale frekvens. Det har lav støjimmunitet. I lavpasfilteret kræves en kondensator med lav lækstrøm. FC2 er bedre egnet til brug i kraftkredsløb med LC-resonans.

Valg af vedhæftede filer

Som et lavpasfilter af lavpasfilteret installeres en modstand R3 og en kondensator C2. For at PLL skal fungere korrekt, skal RC-tidskonstanten være ti gange større end den omtrentlige PLL-indfangningsfrekvens.

Som regel er indfangningsfrekvensen tilnærmelsesvis kendt af udvikleren, derfor indstilles de oprindeligt af frekvensens automatisk indstillingsområde: fmin og fmax. Det første nomogram bestemmer, under hensyntagen til forsyningsspændingen for mikrokredsløbet og den krævede fmin, værdierne af R2 og C1.Derefter vælges R1 i henhold til det andet nomogram baseret på det krævede forhold fmax / fmin. Det er bedre at give mulighed for at justere modstande i kredsløbet.

Se også på elektrohomepro.com

: